ISSUE 9

PM5346 S/UNI LITE

S/UNI-LITE ERRATA NOTICE

PM5346

# S/UNI-LITE

# SATURN USER NETWORK INTERFACE (LITE)

# DATA SHEET ERRATA

ISSUE 9: MARCH 1999

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS' INTERNAL USE

DATASHEET ERRATA PMC-941215

ISSUE 9

S/UNI-LITE ERRATA NOTICE

### **PUBLIC REVISION HISTORY**

| lssue<br>No. | Issue<br>Date  | Details of Change                                                                                                          |

|--------------|----------------|----------------------------------------------------------------------------------------------------------------------------|

| 9            | Sept.,<br>1998 | Revised test mode 0 register settings<br>and clarified the register bits that set<br>INTB. LOOPT bit description modified. |

ISSUE 9

S/UNI-LITE ERRATA NOTICE

### TABLE OF CONTENTS

| 1 | RDO  | OLV BIT OPERATION:       | 1 |

|---|------|--------------------------|---|

| 2 | BRA  | NDING DIAGRAM            | 2 |

| 3 | LOO  | P FILTER RECOMMENDATIONS | 3 |

|   | 3.1  | PAGE 111                 | 3 |

|   | 3.2  | PAGE 113                 | 4 |

| 4 | TES  | ۲ MODE 0                 | 6 |

| 5 | PAGE | Ξ 47                     | 7 |

PM5346 S/UNI LITE

S/UNI-LITE ERRATA NOTICE

#### 1 RDOOLV BIT OPERATION:

Anomolous operation of the RDOOLV bit (Register 0x07, bit 3 on page 50 of the Issue 6 datasheet) has been noticed. Under certain circumstances, the RDOOLV bit may falsely indicate data out of lock.

It is recommended that spurious RDOOLV indications be ignored, and that the RDOOLE bit (Register 0x07, bit 1 on page 50 of the Issue 6 datasheet) be programmed to '0' in order to permanently disable RDOOLV interrupts.

The RDOOLV bit should only be examined as a diagnostic aid in situations where other major on-chip alarms are indicated.

Note: The anomolous RDOOLV only occurs in revisions prior to 'Revision D' of the PM5346 S/UNI-155 LITE. Subsequent revisions, starting with 'Revision D' have this problem corrected. Software work-arounds as indicated above will work with all revisions. For details on identifying the device revision, please refer to the Branding Diagram.

DATASHEET ERRATA PMC-941215

ISSUE 9

S/UNI-LITE ERRATA NOTICE

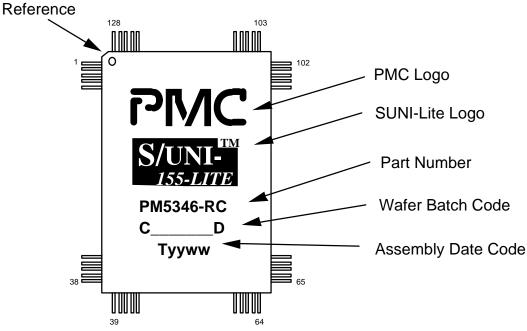

#### 2 BRANDING DIAGRAM

SCALE = 3.2 : 1 (Approx.)

#### Wafer Batch Code has three components:

- One character for wafer fab source (**P or C**)

- Up to 7 characters and/or digits for wafer manufacturer's batch code

- (\_\_\_\_\_

\_\_\_)

• One character for mask set revision (A, C or D). Note: There is no rev. 'B'.

For example "CA123456D" is for source "C" wafers, batch A12345.6, device rev "D"

### Assembly Date Code has three components:

- 1 character for assembly source (T)

- 2 digits for year (yy)

- 2 digits for week (ww)

For example "T9524" is for parts packaged by source "T" in the 24th week of 1995.

ISSUE 9

S/UNI-LITE ERRATA NOTICE

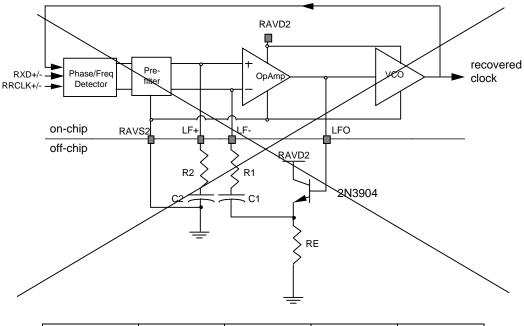

#### 3 LOOP FILTER RECOMMENDATIONS

An extensive analysis of loop filter requirements on the S/UNI-LITE was performed. As a result of this analysis, the following changes are required to the Issue 6 datasheet:

#### 3.1 Page 111

On Page 111 of the Issue 6 datasheet, make the following changes:

#### Clock Recovery

Figures 14a) and 14b) are is an abstractions of the clock recovery phase lock loop illustrating the connections to external components.

Figure 14a illustrates the asymmetrical loop filter application where the external passive components (R1, R2, C1, C2) are set to different values to account for the finite output impedance of the integral op-amp in the S/UNI-LITE. The asymmetrical loop filter circuit <u>provides maximum jitter</u> tolerance without jitter peaking and is recommended for all designs. does not have good jitter transfer properties and is not recommended for new designs.

Figure 14b illustrates the unity gain buffer loop filter application where the integral op-amp output is buffered through a unity gain amplifier to minimize the effect of its finite output impedance on the transfer function of the PLL. The unity gain buffer loop filter circuit exceeds SONET/SDH jitter tolerance and jitter transfer specifications and is recommended for new designs.

Additional analysis of jitter transfer and jitter tolerance issues for the S/UNI-LITE can be found in PMC's ATM Design Notes "Meeting SONET/SDH WAN Interface Jitter Transfer Requirements with the S/UNI-LITE", PMC-950139

DATASHEET ERRATA PMC-941215

ISSUE 9

#### 3.2 Page 113

On Page 113 of the Issue 6 datasheet, make the following changes (delete entire page):

#### Fig. 14b Clock Recovery Circuit - Unity Gain Buffer Loop Filter (recommended for designs requiring BISDN-UNI jitter transfer)

| Line Rate<br>(Mbit/s) | <del>R1</del><br><del>(•±1%)</del> | <del>R2</del><br><del>(•±1%)</del> | <del>C1, C2</del><br><del>min (μF)</del> | <del>RE</del><br>(•±1%) |

|-----------------------|------------------------------------|------------------------------------|------------------------------------------|-------------------------|

| <del>155.52</del>     | <del>68.1</del>                    | <del>90.9</del>                    | <del>4.7</del>                           | <del>100</del>          |

| <del>51.84</del>      | <del>68.1</del>                    | <del>90.9</del>                    | <del>15</del>                            | <del>100</del>          |

The capacitors (C1, C2) determine the amount of "peaking" in the jitter transfer curve. The capacitor values can be  $\pm 10\%$ . The capacitors should be non-polarized because when the S/UNI-LITE is held in reset, the capacitors are reverse-biased at approximately 2.0V. Also, for some process extremes, the capacitors may operate with a D.C. reverse-bias of up to 1.0V.

The recommended values for the capacitors are not readily available in nonpolarized versions. Therefore, two polarized capacitors can be connected "backto-back" (in series, anode-to-anode) to implement each capacitance in Figure

S/UNI-LITE ERRATA NOTICE

14b. Since these back-to-back capacitors will be in series, they should be of twice the value of the desired capacitance. This back-to-back configuration effectively creates a "bi-polar" capacitor.

PMC PMC-Sierra, Inc.

PM5346 S/UNI LITE

S/UNI-LITE ERRATA NOTICE

#### 4 TEST MODE 0

In order to correctly test in Test Mode 0 the following registers must be written with all zeros: 0x9A, 0xB2 and 0xE0.

As well, register 0x96 bit 6 and register 0xD0 bit 0 control the INTB, if either bit is set to a one the output pin is asserted low.

The INTB pin is the NOR of both these register bits.

ISSUE 9

ISSUE 9

S/UNI-LITE ERRATA NOTICE

## 5 PAGE 47

On Page 47 of the Issue 6 datasheet, make the following changes (under LOOPT bit description):

#### LOOPT:

The LOOPT bit selects the source of timing for the transmit section of the S/UNI-LITE. When LOOPT is a logic zero, the transmitter timing is derived from inputs TRCLK+ and TRCLK-.

When LOOPT is a logic one, the transmitter timing is derived form the receiver inputs RXD+ and RXD- when clock recovery is enabled and from RRCLK+ and RRCLK- when clock recover is disabled.

ISSUE 9

S/UNI-LITE ERRATA NOTICE

#### **CONTACTING PMC-SIERRA, INC.**

PMC-Sierra, Inc. 105-8555 Baxter Place Burnaby, BC Canada V5A 4V7

Tel: (604) 415-6000

Fax: (604) 415-6200

Document Information: Corporate Information: Application Information: document@pmc-sierra.com info@pmc-sierra.com apps@pmc-sierra.com (604) 415-4533 http://www.pmc-sierra.com

Web Site:

None of the information contained in this document constitutes an express or implied warranty by PMC-Sierra, Inc. as to the sufficiency, fitness or suitability for a particular purpose of any such information or the fitness, or suitability for a particular purpose, merchantability, performance, compatibility with other parts or systems, of any of the products of PMC-Sierra, Inc., or any portion thereof, referred to in this document. PMC-Sierra, Inc. expressly disclaims all representations and warranties of any kind regarding the contents or use of the information, including, but not limited to, express and implied warranties of accuracy, completeness, merchantability, fitness for a particular use, or non-infringement.

In no event will PMC-Sierra, Inc. be liable for any direct, indirect, special, incidental or consequential damages, including, but not limited to, lost profits, lost business or lost data resulting from any use of or reliance upon the information, whether or not PMC-Sierra, Inc. has been advised of the possibility of such damage.

© 1999 PMC-Sierra, Inc.

PMC-941215 (R9) ref PMC-931110(R6) Issue date: March 1999